Intel Core i7-3770K & DZ77GA‐70K – Ivy Bridge arhitektura i performanse

Datum objave 23.04.2012 - Krešimir Matanović

Intel 22nm tehnologija i tri-gate tranzistori

Sandy Bridge je kao što znamo donio bitne arhitekturalne izmjene u odnosu na prvu Intelovu Core generaciju procesora i on je predstavljao Tock u njihovom Tick-Tock proizvodnom roadmapu. Sada je red došao na sljedeći Tick i ta je nova generacija procesora poznata pod kodnim imenom Ivy Bridge (po Ivy mostu preko rječice Erme u gradu Ivybridge Engleskoj). No ovaj Tick i nije čisti Tick, jer Intel osim novog proizvodnog procesa i korištenja novog tipa tranzistora, donosi i arhitekturalne promjene u grafičkom dijelu procesora o kojima ćemo nešto kasnije. Sada ćemo se koncentrirati na prijelaz sa 32 na 22 nm proizvodni proces i naravno tranzistore koji umjesto jednih imaju troja vrata za propuštanje ili blokiranje toka struje.

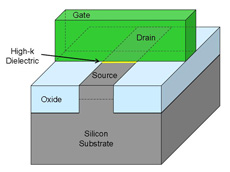

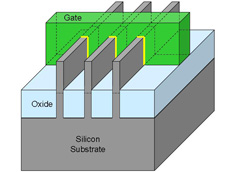

22 nm proizvodni proces nosi kodno ime P1270, te je prva proizvodnja započeta još 2011. godine. Procesi koji slijede su P1272 (14 nm, 2013.) i P1274 (10 nm, 2015.). Smanjenjem procesa na 22 nm proizvođači su naletjeli na zid koji kaže kako ekvivalentna debljina oksida fizički ne može skalirati ispod 0.5 nm, što dovodi do velikog otjecanja struje kada su vrata tranzistora zatvorena. Stoga su u Intelu osmislili novi pristup cijeloj priči i odbacili klasične planarne tranzistore koji se sastoje od izvora, jednih vrata i odvoda. U proizvodnju su uveli tranzistore koji imaju troja vrata te klasično jedan izvor i jedan odvod. Ono što su zapravo napravili je da su podigli silicijsku podlogu u sama vrata, i to na tri mjesta te su time dobili tranzistor sa troja vrata. Time su osigurali bolju kontrolu otjecanja struje kada su vrata zatvorena, zbog činjenice da sada zatvorena vrata mogu s tri strane izgurati slobodne elektrone iz provodnog kanala. time su osigurali strmiji nagib krivulje praga otvaranja tranzistora. To je pak dovelo do toga da je moguće koristiti niže radne napone i povećati brzinu prebacivanja iz stanja u stanje. Upravo to je razlog zbog kojeg Ivy Bridge procesori imaju niži radni napon od Sandy Bridgea, čime im se naravno i TDP smanjuje. Ono što je također bitno za naglasiti je da se kod planarnih tranzistora brzina prebacivanja smanjuje sa snižavanjem napona, i da bi se prelaskom na 22 nm proizvodni proces kod njih to uspjelo donekle riješiti (oko 18% manji gate delay). Uvođenjem pak tri-gate tranzistora na 22 nm procesu, gate delay se smanjuje za oko 37% u odnosu na 32 nm planare i to pri 0.2V nižem naponu. Kod Tri-gate tranzistora se uz to smanjuje i varijabilnost zbog suženja (smanjenja) vodljive površine kanala, te se smanjuje osjetljivost stope Soft Error-a (greške u signalu). Sve ovo dolazi uz povećanje proizvodnih troškova od oko 2-3% što je Intelu bilo sasvim prihvatljivo kako bi nastavio s praćenjem Mooreovog zakona.

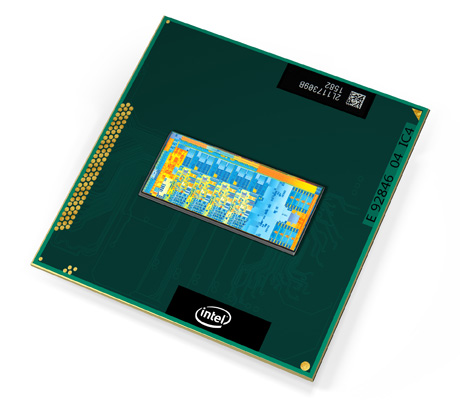

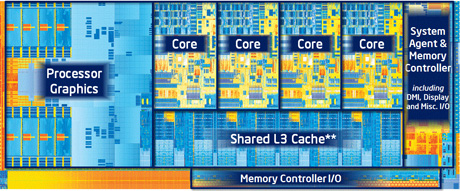

Iz svega toga je rođena nova Ivy Bridge jezgra koja u odnosu na Sandy Bridge donosi povećanje u broju tranzistora od oko 20.5% (1.4 vs. 1.16 milijarde tranzistora), te istovremeno smanjenje površine za oko 24.5% (sa 212 mm2 na 160 mm2). Ivy Bridge procesori se za sada proizvode na tri lokacije, tj. u tri Fab-a – D1D Oregon, Fab 32 Arizona i Fab 28 Israel, dok su D1C Oregon i Fab 12 Arizona u planu. 22 nm proizvodi će se u budućnosti naći u širokom spektru proizvoda, od mobilnih uređaja, preko desktopa pa do servera. Zanimljivo je kako povijest tri-gate tranzistora u Intelu kreće još 2003. godine, kada su prvi put proizveli single-fin tranzistor, da bi 2006. proizveli prve tri-gate SRAM ćelije i konačno 2010. godine u potpunosti optimizirali tri-gate tehnologiju za proizvodnju. To govori koliko se unaprijed proizvođači pripremaju za daljnja smanjenja proizvodnih procesa koja sa sobom donose u daljnje prepreke.

Ivy Bridge

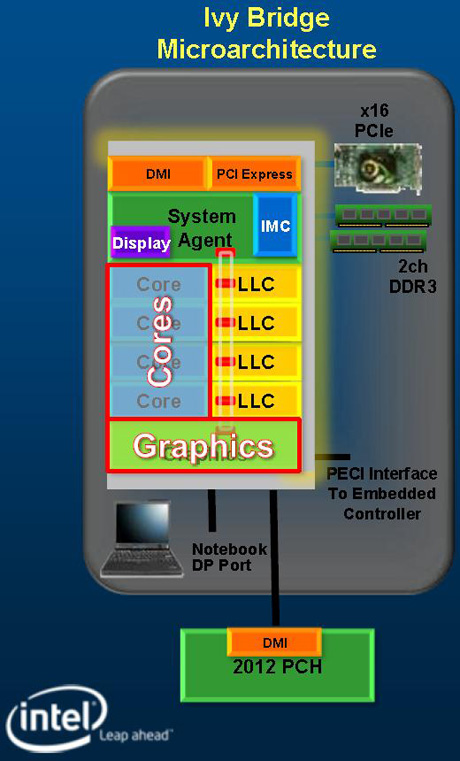

Novosti koje Ivy Bridge arhitektura donosi u arhitekturalnom smislu su nove ISA ekstenzije, nove značajke upravljanjem potrošnje električne energije, nove sigurnosne značajke, nove I/O značajke te poboljšanje performansi. Ovo sve se još ne odnosi na promjene u grafici kojih ćemo se dotaknuti kasnije. Arhitektura IB-a je fundamentalno identična SB-u, pa tako Intel i dalje nastavlja sa platformom dva čipa (CPU + PCH), pri čemu na CPU-u donosi potpunu integraciju 2 do 4 procesorske jezgre, grafičku jezgru sa media i display mehanizmima, memorijski kontroler, PCIe kontrolere, modularnu On-Die Ring Interconnect arhitekturu te dijeljeni LLC (Last Level Cache). Ivy Bridge se proizvodi na istom LGA1155 socketu kao i Sandy Bridge, pri čemu su međusobno unazad kompatibilni.

Novosti su da je cijeli čip preseljen na 22 nm proizvodni proces, novi su setovi instrukcija (Float16, Fast FS/GS podrška, REP MOVSB i RDRAND). Sigurnosna poboljšanja uključuju DRNG (Digital Random Number Generator) i SMEP (Supervisory Mode Execute Protection). Sa strane poboljšanja upravljanja potrošnjom energije tu su DDR I/O Embedded Power Gating (EPG), koji isključuje dio I/O-a memorije tijekom dubokih C-stanja. Intel očekuje kako će tijekom Idle/MM07-OP stanja I/O vrata biti oko 90% ugašena pri čemu su moguće uštede od 70 do 100 mW. Ovo povećava latenciju za oko 5 – 10 mikro sekundi, ali treba znati kako je proces potpuno automatiziran i kako se EPG neće koristiti kod aplikacija koje ne mogu podnijeti tu ekstra latenciju. Uz ovo, dodan je i PAIR algoritam koji snižava snagu i utjecaj na pad performansi kod re-routable interupta. PAIR uspoređuje stanja snage svih jezgri te bira onu najbolju (na bazi C i P stanja pojedine jezgre, koristeći IA32_PERFORMANCE_BIAS MSR) za odrađivanje interupta.

Sa strane menadžmenta energijom tu je i konfigurabilni TDP koji omogućuje različite razine TDP-a unutar procesora, uz korištenje Low Power moda koji definira najnižu aktivnu operativnu točku za pojedini dio procesora. Obje se znčajke mogu implementirati softverski, a način na koji će se koristiti ostavljen je na izbor OEM-u ili krajnjem korisniku. Ivy Bridge donsi i integrirane PCIe kontrolere treće generacije (PCI Express Gen 3), koji donose gotovo duplo veću propusnost u odnosu na Gen 2, te time poboljšava performanse aplikacijama koje su osjetljive na I/O propusnost. Sa strane integriranog memorijskog kontrolera nosvosti su podrška za Low voltage DDR3 (DDR3L) i povećanje brzina na 1600MHz uz mogućnost korištenja i znatno viših memorijskih množitelja (u nekim slučajevima do 28).

Najznačajnija IPC (Instruction per Clock) uključuju MOV (Move mikro operacije) iz izvršnog pipelinea procesora, uvođenje pipeline djelitelja (poboljšava propusnost računskih operacija povezanih s dijeljenjem), zatim uvođenje Next page prefetchera (prefetchig se može proširiti i preko granice od 4K po stranici), zatim uvođenje Shift/Rotate-a te šest dodatnih split load registara. Uncore IPC značajke su AFP (Adaptve Fill Policy – heuristika cache-a za odvajanje streaming aplikacija), QLRU (Quad-Age LRU algoritam koji povećava broj starosnih stanja zahtjeva u alociranju cache-a), zetim DPT (Dynamic Prefetch Throttling koji je zapravo real-time nadzor za propusnost memorije, te smanjuje prefetch "agresivnost" tijekom visokih opterećenja memorije) i na kraju Channel Hashing, tj. mehanizam za odabir DRAM kanala (omogućava jednakiju distribuciju pristupa memoriji preko kanala).

Vjerovali ili ne, IVy Bridge doonsi i poboljšanja u overclockingu. Iako je BCLK restrikcija zadržana, povećan je Bclk/Core odnos, tj. množitelj na 63:1, poboljšana je overlocking logika DDR-a na 2800MT/s. te su dodani finiji koraci u podešavanju memorijske frekvencije (umjesto standardnih 266MHz koraci su sada 200MHz, što omogućava brzine poput 2000MHz koje kod SB-a nisu bile moguće).

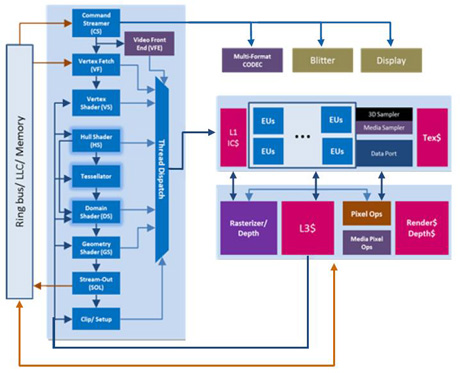

Unatoč svim promjenama koje su zahcarile core i uncore dio procesora, to još uvijek nije dovoljno da bi se smatralo ičim više od Ticka. Prave izmjene su se pak desile na grafičkom dijelu, i njega Intel naziva Tick+. Promjene su zahvatile arhitekturu, mikro arhitekturu i menadžment potrošnjom energije. Intel ovaj dio procesora zove Graphics i Media, zbog poznatog Quick Sync Video mehanizma. Grafički dio donosi povećanje u performansama, te DX11 podršku (ne i DX11.1), dok je Quick Sync također znatno ubrzan. Velika novost je i nativna podrška za tri monitora. Mikso arhitektura je skalabilna, te je podijeljena u pet domena: Global Assets (geometrijski front-end), Slice Common (rasterizator, L3$ i piksel back-end), Slice (shaderi (EU), IC$, sampleri i generator adresa), CODEX & media, te Displays. Ovakav način particioniranja, otvara mogućnost daljnjeg povećanja grafičke jedinice pa u budućnosti možemo vidjeti i naprednija rješenja od Intela (više EU-a npr). Nadalje, popravljene su geometrijske performanse (brži GS i H/w Stream out, brži Clip/Setup), poboljšana je Anisotropic kvaliteta, zatim compute throughput (peak GFLOPS), itd. Quick Sync Video je ubrzan povećanjem performansi za Multi-Format CODEC, povećana je propusnost Media Samplera, a Pixel Back ima Image Color i Contrast Enhancement mogućnosti.

Podrška za DX11 donosi hardversku teselaciju (dodane dvije programabilne faze – HS i DS, te fixed function teselator). Tu je i podrška za format kompresiranja tekstura BC6H/7. Bitna izmjena u arhitekturi je i dodavanje Compute Shader podrške (Data Parallelism, UAVs, Atomics, Barriers, itd za compute shader operacije, zatim Shared Local Memory aka Thread Group Local Memory for Direct Compute Shaders, te Scatter gather).

Sa strane optimizacija potrošnje električne energije, 22 nm mikro arhitektura je donijela upola manju potrošnju za iste performanse ili poduplane performanse po wattu potrošnje. Co-issue je proširen na EU (Execution unit), a više je IPC snage po površini donijelo manje curenja struje. Zadnje i ne manje bitno je da je snižen zahtjev za bandwidthom iz LLC-a čime se također smanjuje potrošnja energije.

Forum

Objavljeno prije 13 minuta

Dobra klimaObjavljeno prije 14 minuta

Linux OS - info, how-to, pitanja, novosti, savjeti, problemi...Objavljeno prije 18 minuta

K:AMD Athlon-64 X2 Dual-Core Processor Socket 939Objavljeno prije 25 minuta

AutomobiliObjavljeno prije 36 minuta

Koji mobitel kupiti? - 2. dioNovosti

.debug 2025 – Tehnološki spektakl u Zagrebu

Već dobro uhodana konferencija .debug, koju organizira magazin Bug u suradnji s vodećim domaćim i međunarodnim tehnološkim kompanijama, i ove se godine pokazala kao središnji događaj hrvatske IT scene. Tijekom dvodnevne, sadržajem vrlo boga... Pročitaj više

IT entuzijasti za zajednicu: Priča o suradnji CRATIS-a i PC Eksperta

Varaždinska IT tvrtka Cratis, specijalizirana za izgradnju i upravljanje visoko dostupnim cloud i hosting sustavima, omogućila je PC Ekspertu besplatno korištenje vlastite enterprise infrastrukture kao oblik podrške domaćoj tehnološkoj i ha... Pročitaj više

AMD predstavlja viziju otvorenog AI ekosustava

AMD) je na svom događaju Advancing AI 2025. predstavio svoju sveobuhvatnu, cjelovitu integriranu viziju AI platforme i svoju otvorenu, skalabilnu AI infrastrukturu u racku izgrađenu prema industrijskim standardima. AMD i njegovi partneri pr... Pročitaj više

Pametni savjeti za zdravu i štedljivu upotrebu klime

Pametno korištenje klime = ugodnije ljeto, manji računi i zdraviji zrak u kući. Zaboravite stare navike i koristite tehnologiju kako treba – klima je vaš saveznik, ne neprijatelj! 1. Držite temperaturu između 25-28°C - 26°C je optimalno –... Pročitaj više

Stvari koje tiho “pojedu” životni vijek SSD-a

Ako ne želite da vam SSD jednog dana samo prestane raditi bez najave, bacite oko na ove savjete. SSD-ovi su stvarno brži i otporniji od starih mehaničkih diskova (HDD), ali imaju jednu veliku manu – ograničen broj ciklusa pisanja. A da stva... Pročitaj više

Sve novosti